что такое программируемая логика

ПЛИС — интегральные схемы программируемой логики

Логические устройства подразделяются на две категории: фиксированной логики и программируемые. Как следует из названия, устройства с фиксированной логикой выполняют одну (либо набор) функций, которые невозможно изменить после их изготовления. Программируемые устройства также являются стандартными изделиями, которые обладают широким диапазоном логической емкости, скорости переключения, входных и выходных напряжений, и их предназначение может быть изменено в любое время для реализации произвольной функции.

Основные понятия ПЛИС

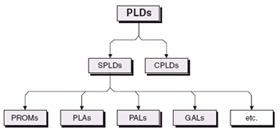

В русскоязычной литературе любую программируемую логику принято называть термином ПЛИС (программируемая логическая интегральная схема). В англоязычной литературе принято различать следующие разновидности программируемых микросхем: PLA, PAL, GAL, SPLD, CPLD, ASIC, FPGA, FPAA, FPID, SoCи т.д.

ПЛИС PLA (Programmable Logic Array)

ПЛИС PAL (Programmable Array Logic)

ПЛИС GAL (Generic Array Logic)

Устройства PAL и PLA – однократно программируемые, их конфигурация не может быть изменена; в отличие от них микросхемы GAL основаны на EEPROM и могут реконфигурироваться. Микросхемы GAL были изобретены Lattice Semiconductor. Аналогичные устройства, PEEL (programmable electrically erasable logic), были предложены International CMOS Technology (ICT).

ПЛИС SPLD (Simple Programmable Logic Devices)

В англоязычной литературе микросхемы PROM, PAL, PLA, GAL принято обобщать термином SPLD.

Существенный прорыв в разработке ПЛИС произошел в 1984г., когда компания Altera предложила CPLD, применив сочетание CMOS и EPROM технологий. Использование технологии CMOS позволило достичь значительной функциональной плотности и сложности при сравнительно небольшом потреблении энергии, а ячейки (англ. cells) EPROM оказались идеальным средством для использования их при разработке и создании прототипов оборудования.

ПЛИС ASIC (Application Specific IC)

ПЛИС FPGA (Field Programmable Gate Array)

Разновидность ПЛИС, содержащая логические элементы и блоки коммутации. Программа для FPGA хранится в распределённой оперативной памяти микросхемы, поэтому требуется начальный загрузчик.

Развитие архитектур ПЛИС привело к созданию комбинированных структур сочетающих достоинства FPGA и CPLD – например, семейство FLEX (Flexible Logic Element Matrix) от Altera.

ПЛИС FPAA (Field Programmable Analog Array)

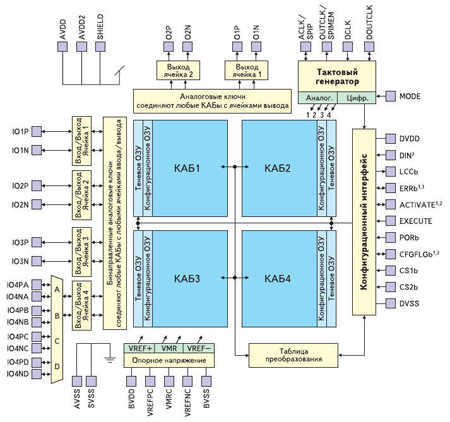

Традиционно схемы аналоговой обработки сигналов выполняются на дискретных компонентах. В ряде случаев аналоговая часть занимает значительную площадь печатной платы и требует сложной настройки. Решить проблему создания аналоговых устройств (иногда для определенной полосы частот спектра) позволяет использование программируемых аналоговых микросхем. На настоящий момент крупнейшим производителем таких микросхем является компания Anadigm.

ПЛИС FPID (Field Programmable Interconnect Device)

Эти программируемые логические интегральные схемы содержат программируемые соединения и блоки ввода/вывода, но не содержат логических блоков. Они предназначены для произвольного соединения своих внешних выводов в соответствии с заложенной программой. При отработке прототипов и при создании динамически конфигурируемых систем такие микросхемы весьма полезны. Соединяя ПЛИС через FPIC можно легко варьировать их межсоединения, чего не обеспечивают технологии с жесткой трассировкой (печатные платы и др.).

ПЛИС SoC (System on Chip)

Применение ПЛИС

ПЛИС SPLD

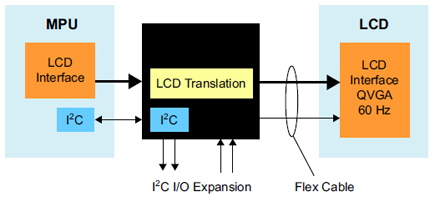

Микросхемы SPLD по-прежнему выпускаются многими производителями. Среди них есть и такие всемирно известные корпорации, как Texas Instruments, NXP, Lattice. У Lattice такие компоненты называются «mature devices», т. е. зрелые, продуманные. Для программирования логических интегральных схем SPLD были разработаны специальные программы (логические компиляторы) для перевода булевых уравнений, таблиц истинности или диаграмм состояний в так называемый файл JEDEC* — закодированный в стандартизированной форме список плавких перемычек, которые следует уничтожить. В дальнейшем, при появлении новых типов ПЛИС, логические компиляторы стали называться языками HDL (Hardware Description Language). На сайте NXP приведены варианты использования компонентов SPLD, в AN036 рассматривается применение микросхемы PLC42VA12 в контроллере расширителя интерфейса I 2 C.

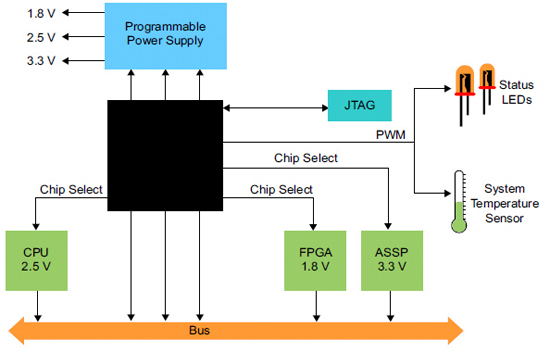

Компания Altera предлагает несколько вариантов применения CPLD серии MAX V**:

1. ПЛИС CPLD применяется для расширения количества портов ввода/вывода других стандартных устройств.

2. Программируемые логические интегральные схемы CPLD применяются для создания мостов (bridge’s) между интерфейсами, т. е. для соединения друг с другом несовместимых по протоколам устройств.

3. Так же ПЛИС CPLD применяется для управления последовательностью включения источников питания и мониторинга других устройств.

4. Программируемые логические интегральные схемы CPLD могут быть использованы для управления конфигурацией или инициализацией других устройств.

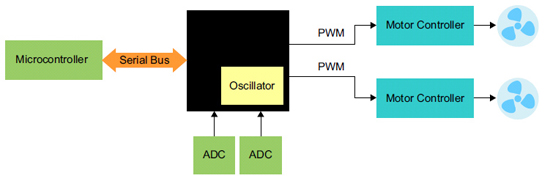

5. ПЛИС CPLD для управления стандартными аналоговыми устройствами в цифровом формате посредством широтно-импульсной модуляции (ШИМ) без применения ЦАП. LUT-архитектура CPLD, выходы с высокой нагрузочной способностью и внутренний генератор микросхемы позволяют обеспечить прямое соединение этой микросхемы с различными стандартными аналоговыми продуктами при использовании ШИМ.

————————————

*JEDEC Standard JESD3-C, Standard Data Transfer Format Between Data Preparation System and Programmable Logic Device Programmer, June 1994.

**Altera, WP-01146-1.2

Что такое FPGA? Введение в программируемую логику

Рассмотрим аппаратный подход к выполнению вычислений, маршрутизации цифровых сигналов и управлении встраиваемыми системами с помощью программируемой логики и FPGA (Field-Programmable Gate Array, программируемой пользователем вентильной матрицы).

FPGA – это программируемая логическая матрица. По своей сути, FPGA представляет собой массив взаимосвязанных цифровых подсхем, которые реализуют общие функции, а также предлагают очень высокий уровень гибкости. Но полная картина того, что такое FPGA, требует большего разбирательства. В данной статье представлены концепции FPGA и кратко обсуждается, что такое логические элементы, как программировать FPGA, и что отличает FPGA от микропроцессоров в плане разработки.

FPGA против микроконтроллера (Или зачем использовать FPGA, когда будет работать и микроконтроллер?)

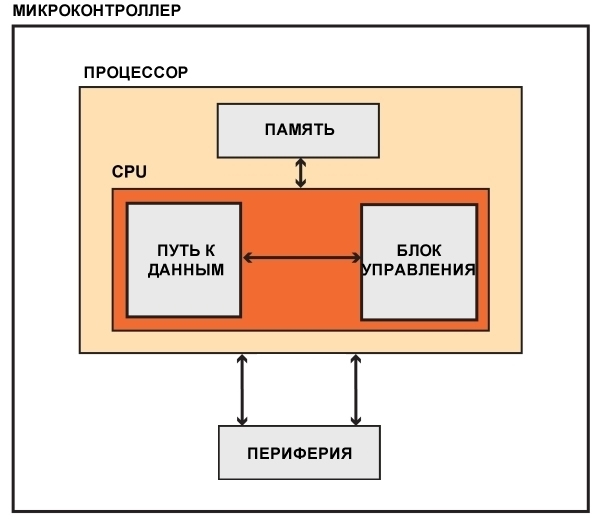

Я думаю, мы все можем согласиться с тем, что микроконтроллеры стали доминирующим компонентом в современных электронных проектах. Они недорогие и универсальные, и в наши дни они часто служат первым в мире знакомством с миром электроники. Естественно, что мы продолжаем использовать компоненты, с которыми знакомы, и поскольку микроконтроллеры становятся всё более мощными, всё меньше и меньше нужно рассматривать альтернативные решения для наших задач проектирования. Тем не менее, микроконтроллер построен вокруг процессора, а процессоры имеют фундаментальные ограничения, которые необходимо признать и в некоторых случаях преодолеть.

Итак, когда инженер предпочтет FPGA микроконтроллеру? Ответ сводится к программному обеспечению и аппаратным средствам.

Процессор выполняет свои задачи, выполняя инструкции последовательно. Это означает, что операции процессора, по сути, ограничены: требуемая функциональность должна быть адаптирована к доступным инструкциям, и в большинстве случаев невозможно одновременно выполнять несколько задач обработки.

Набор инструкций рассчитан на высокую универсальность, и в настоящее время инструкции могут выполняться на чрезвычайно высоких частотах; однако эти характеристики не устраняют недостатки программного подхода к цифровому проектированию.

Альтернативой является аппаратный подход. Было бы чрезвычайно удобно, если бы каждый новый проект мог быть построен вокруг цифровой микросхемы, которая в точности реализует функциональность, требуемую системой: нет необходимости писать программное обеспечение, никаких ограничений набора команд, никаких задержек обработки, только одна микросхема, которая имеет входные выводы, выходные выводы и цифровую схему, в точности соответствующую необходимым операциям. Эта методология нецелесообразна вне описания, поскольку она предполагает разработку ASIC (application-specific integrated circuit, специализированной интегральной микросхемы) для каждой платы. Однако мы можем аппроксимировать эту методологию, используя FPGA.

Что такое программируемая пользователем вентильная матрица?

Хорошее название может быть довольно информативным, и я бы подумал, что «программируемая пользователем вентильная матрица» («field-programmable gate array») будет достаточно хорошим названием. FPGA – это матрица логических вентилей (ну вроде – смотрите ниже) и эта матрица может быть запрограммирована (на самом деле, «сконфигурирована», вероятно, более подходящее слово) в поле, то есть пользователем устройства, как противоположность людям, которые его разработали. Давайте посмотрим на основные характеристики.

Логические вентили (элементы) (И, ИЛИ, исключающее ИЛИ и т.д.) являются основными строительными блоками цифровой схемы. Поэтому неудивительно, что цифровое устройство, которое должно быть чрезвычайно конфигурируемым (то есть «field-programmable» / программируемым в поле / программируемым пользователем), будет состоять из множества вентилей, которые могут быть связаны между собой настраиваемым способом.

Однако FPGA не является огромной коллекцией отдельных булевых элементов. Это было бы очень неоптимальным способом обеспечения функциональности конфигурируемой логики, потому что не использовало бы тот факт, что распространенные операции могут быть реализованы гораздо эффективнее как фиксированные модули. Тот же принцип проявляется и в мире дискретных цифровых микросхем. Вы можете купить микросхемы, которые состоят из элементов И, элементов ИЛИ и т.д., но вы не захотите создавать сдвиговый регистр из отдельных элементов. Вместо этого вы купите микросхему сдвигового регистра.

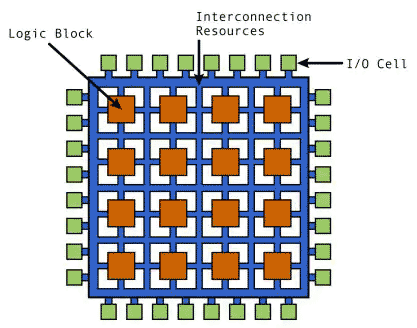

Конфигурируемые логические блоки (CLB) должны взаимодействовать друг с другом и с внешней схемой. Для этих целей FPGA использует матрицу программируемых межсоединенй и блоков ввода/вывода (I/O). «Программа» FPGA хранится в ячейках SRAM, которые влияют на функциональность блоков CLB и управляют коммутаторами, которые устанавливают пути подключения.

Подробное объяснение внутренней структуры и работы блоков CLB потребует целой статьи (если не нескольких статей). Общая идея заключается в том, что CLB включают в себя таблицы поиска, элементы хранения (триггеры и регистры) и мультиплексоры, которые позволяют CLB выполнять логические операции, операции хранения данных и арифметические операции.

Блок ввода/вывода состоит из различных компонентов, которые облегчают связь между CLB и другими компонентами на плате. К ним относятся подтягивающие резисторы, буферы и инверторы.

Программируемая пользователем логика (Или как вы программируете FPGA?)

Как мы собираемся превратить массив настраиваемых логических блоков (CLB, Configurable Logic Block) в цифровую схему, которая делает именно то, что мы хотим? На первый взгляд это кажется довольно сложной задачей. Действительно, реализация FPGA обычно считается сложнее, чем программирование микроконтроллера. Однако разработка для FPGA не требует глубокого знания функциональности CLB или кропотливой компоновки внутренних межсоединений, так же как разработка для микроконтроллеров не требует глубокого знания инструкций на языке ассемблера процессора или внутренних сигналов управления.

На самом деле, несколько неверно представлять FPGA как самостоятельный компонент. FPGA всегда поддерживаются программным обеспечением для разработки, которое выполняет сложный процесс преобразования аппаратного проектирования в программируемые биты, которые определяют поведение межсоединений и CLB.

Это оставляет нам важный вопрос: как мы «объясним» программе, что должно делать аппаратное обеспечение FPGA?

Языки описания аппаратных средств

Оказывается, люди создали языки, которые позволяют нам «описывать» аппаратное обеспечение, они называются (очень соответствующе) языки описания аппаратных средств (HDL, hardware description language), а два наиболее распространенных – VHDL и Verilog. Несмотря на очевидное сходство между HDL кодом и кодом, написанным на языке программирования высокого уровня, они принципиально отличаются друг от друга. Код программы определяет последовательность операций, тогда как HDL код больше похож на схему, которая использует текст для представления компонентов и создания взаимосвязей.

Заключение

Надеюсь, теперь вы понимаете основные характеристики устройств программируемой логики и их потенциальные преимущества в отношении процессорных систем. Современные FPGA – это сложные, высокопроизводительные устройства, которые могут быть несколько пугающими для тех, кто привык использовать микроконтроллеры для сбора данных, управления микросхемами специального назначения и выполнения математических операций. Однако вы можете обнаружить, что в некоторых приложениях улучшенная производительность и универсальность стоят дополнительных усилий в разработке.

А в ближайшее время на RadioProg появится несколько статей, помогающих начать разработку на FPGA.

Начинаем работать с FPGA или ПЛИС это просто. Часть 1

ВВЕДЕНИЕ

Из доступных бюджетных ПЛИС можно выделить двух основных производителей Altera и Xilinx, с их продукции можно начать свой путь освоения данных технологий. На мой взгляд лучше выбрать чипы компании Altera, так как их среда проектирования стабильно обновляется, а выбрав один популярный чип Xilinx XC3S500E вам придется довольствоваться устаревшей средой ISE 14.7 (хотя и там есть свои плюсы).

Разговор пойдет о более простых вещах, тем более ко мне в руки попал набор разработчика: Cyclone IV 4 FPGA Core Board и Altera USB Blaster Downloader PLD Development kit за 35$, приобретенный на AliExpress.

1 Демоплата Cyclone IV 4 FPGA Core Board, краткая характеристика

На плате (Рис. 1) установлен чип EP4CE6E22C8N, его характеристики:

На плате установлено:

В комплекте также идет программатор JTAG, Altera USB Blaster.

2. Среда Quartus II и наш первый проект

И жмем кнопку скачать (Download Selected Files). После чего нам предложат зарегистрироваться, регистрируемся, скачиваем и устанавливаем.

Создадим свой первый проект.

Жмем next, у нас спрашивают, пустой проект (empty project) или шаблон (Project template). Оставляем пустой, next. Дальше нас просят добавить существующие файлы, у нас ничего нет, поскольку мы только начинаем свой путь, жмем next.

Далее нам необходимо выбрать наш чип, это можно сделать в любое время. Выбираем как на рисунке, Family – Cyclone IV E, specific device selected in “Available devices” и выбираем наш чип EP4CE6E22C8N, он в самом начале. Если у вас другой, найдите свой, это важно. Жмем next.

В окне выбираем пункт «Unused pins». Эта настройка определяет, что будет с неподключенными пинами. Это может быть важно, в своем проекте вы вряд ли используете все пины, а не подключенные могут быть на деле соединены с землей или питанием (ну мало ли, кто разводил плату). Если вы подадите единичку на заземленный пин, то он сгорит, поэтому нужно внимательно следить за этим.

Далее нам нужно настроить пины, это нужно чтобы сигнал шел на нужные нам ножки чипа, ведь изначально Quartus не знает, что куда подключено и как именно осуществлена разводка платы.

Подключаем это все в «Assignment Editor»

В появившемся окне делаем как у меня, ну или если совсем правильно, то согласно схеме вашей платы.

В колонке «To» вписываем имя входа или выхода. В колонке «Assignment Name» выбираем «Location». В колонке «Value» номер контакта микросхемы, согласно схемы платы (у меня номера пинов написаны прямо на плате).

Также нужно указать, что делать с кнопками, которые одной ногой подключены к земле, а другой ко входу чипа. При нажатии на ноге будет низкий уровень, а вот без нажатия, непонятно, нога чипа будет просто висеть в воздухе, что очень плохо. Нужно подтянуть к питанию вход чипа либо резистором на плате, либо боле элегантным способом в «Assignments Editor». В колонке «Assignment Name» выбираем «Weak Pull Up resistor» для группы key* (группа обозначается через звездочку).

Далее нужно создать описание модуля верхнего уровня, который будет работать непосредственно с ножками чипа, все остальные модули будут работать только с ним. В главном меню жмем New, и выбираем «Design Files-> Block Diagram/Schematic File».

В открывшемся окне выбираем инструмент «Pin Tool» и располагаем вход и выход (пины ввода и вывода) на диаграмме. Переименовываем вход как key[0], выход как led[0] и соединяем их проводником. Сохраняем и нажимаем «Start Compilation».

После компиляции у нас возникли предупреждения, пока игнорируем их, они касаются неподключенных пинов, отсутствия тактового сигнала и описания для «Timing Analyzer».

Подключаем демоплату и программатор, выбираем инструмент «Programmer». В окне должно значиться «USB-Blaster [USB-..]», если нет то нажимаем «Hardware Setup» и пытаемся разобраться почему нет, скорее всего не установлены драйвера, смотрим в устройства Windows, ищем неопределенные устройства, может с кабелем проблема. Если все хорошо нажимаем «Auto Detect» и выбираем наш чип.

Нажимаем двойным щелчком мыши в поле «File» и выбираем файл для записи на ПЛИС (находиться в папке output_files нашего проекта), ставим галочку в поле «Program / Configure», и нажимаем кнопку «Start».

Поздравляю с первой конфигурацией ПЛИС! Диод D1 должен светиться, при нажатии key1 должен гаснуть (так как кнопка замыкает ножку с землей), далее мы с этим что-нибудь сделаем)

Программируемая логика выводит решения на базе микропроцессоров на новый уровень гибкости и скорости разработки

Джек Шандл, Mouser Electronics

Вступление

Возможности и скорость работы программируемых логические устройств, таких как программируемые пользователем логические матрицы, или ППЛМ (Field-Programmable Gate Array, FPGA), программируемые логические интегральные схемы, или ПЛИС (Complex Programmable Logic Device, CPLD), существенно возросли с момента их появления на рынке в качестве замены дискретной логики и средства прототипирования специализированных интегральных схем (Application-Specific Integrated Circuit, ASIC). Встроенные микропроцессоры и аппаратные ускорители позволяют успешно применять их даже в областях, где раньше безоговорочно доминировали цифровые сигнальные процессоры – ЦПС (Digital Signal Processor, DSP) и специализированные микросхемы (Application Specific Standard Product, ASSP). Усвоив основные принципы работы ППЛМ и ПЛИС, разработчики могут повысить производительность и эффективность своих решений, оптимизировать циклы их разработки.

Перед тем как обрести формы архитектур ППЛМ и ПЛИС, программируемая логика прошла длинный путь. Различие между данными архитектурами отражается в их названии. Программируемые пользователем логические матрицы (Field-Programmable Gate Array) имеют структуру, аналогичную матрице специализированных вычислительных элементов. По факту они предназначались именно для прототипирования ASIC. Программируемые логические интегральные схемы состоят из массива однотипных логических программируемых элементов.

Основы программируемой логики

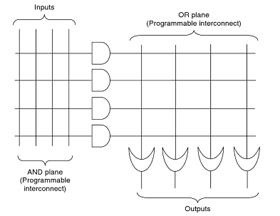

Основную идею конфигурации ППЛМ и ПЛИС можно легко понять, оглядываясь на организацию программируемых логических массивов, или ПЛМ (Programmable Array Logic, PAL), которые представляли собой набор программируемых входов, объединяемых по «И», а слой с элементами «ИЛИ» являлся фиксированным, что ограничивало количество термов, которые можно было реализовать. В их состав также были включены базовые логические устройства, такие как мультиплексоры, исключающее «ИЛИ» и триггеры-защелки.

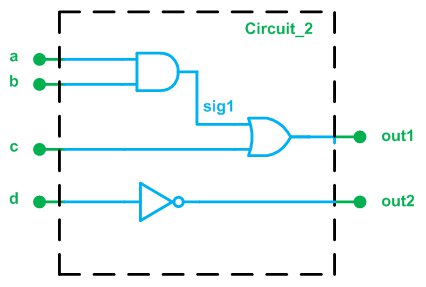

Подобная комбинация элементов и соединений позволяет разработчику реализовать большое количество логических функций, включая последовательностные схемы, необходимые для конечных автоматов. ПЛМ – очень быстрые устройства, заменяющие схемы предыдущего поколения на дискретных элементах. Рис. 1 демонстрирует базовый элемент ПЛМ, в котором программируемые элементы (изображенные как плавкие предохранители) соединяют прямые и инверсные входы с элементами «И», а выходы элементов «И» объединяются вместе по «ИЛИ», формируя тем самым на выходе логическую функцию.

ПЛИС и ППЛМ являются золотой серединой между ПЛМ и ASIC. ПЛИС практически такие же быстрые, как ПЛМ, но их структура не столь проста. ППЛМ имеют более сложные программируемые элементы и являются реконфигурируемыми.

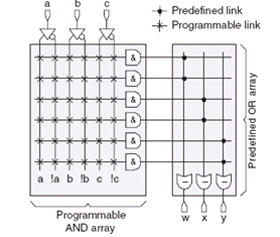

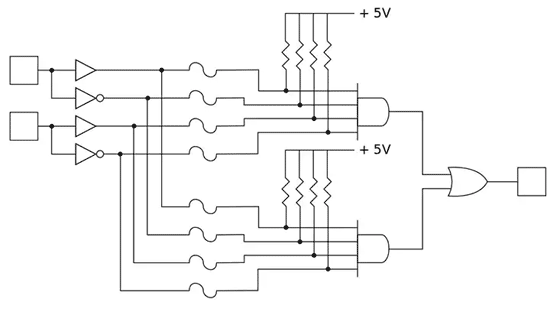

Архитектура ПЛИС

Несмотря на то, что каждый производитель ПЛИС реализует свою собственную технологию, все ПЛИС имеют общие характерные черты и состоят из набора функциональных блоков (ФБ), блоков ввода-вывода и коммутационной матрицы. Программируются ПЛИС элементами, специфичными для каждого производителя. Элементами конфигурационной памяти могут быть ячейки EPROM, EEPROM или Flash EEPROM. На рис. 2 представлена типичная архитектура ПЛИС.

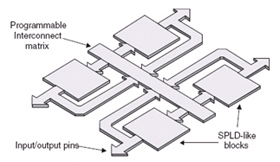

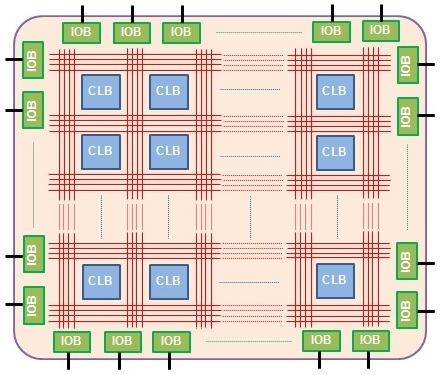

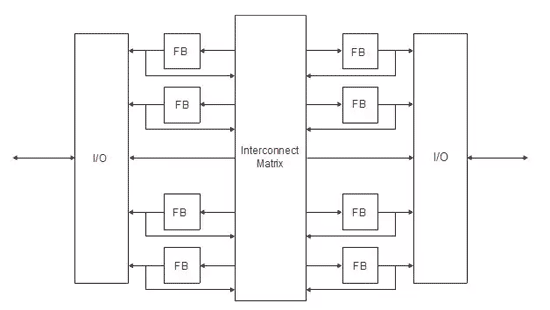

Архитектура ППЛМ

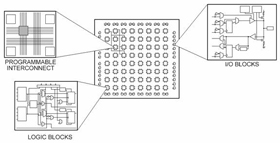

Архитектура ППЛМ близка к архитектуре ASIC и отличается от ПЛИС. В общем случае ППЛМ состоит из конфигурируемых логических блоков (КЛБ), блоков ввода-вывода и программируемой схемы соединений (рис. 3). К каждому логическому блоку подведены тактирующие сигналы. Также типовыми элементами для ППЛМ являются арифметические элементы, блоки памяти и декодеры. Логика в ППЛМ реализуется в КЛБ, который содержит ОЗУ (известное как таблицы поиска – lookup tables, LUTs) для задания комбинационных логических функций. КЛБ также содержат триггеры-защелки и мультиплексоры для соединения логики в пределах блока и с внешними ресурсами. Мультиплексоры также используются для коррекции логического уровня сигнала, подведения сигнала сброса.

|

| Рис. 1. Упрощенная структура программируемого логического массива. |

|

| Рис. 2. Типовая структура ПЛИС. |

|

| Рис. 3. Типовая структура ППЛМ. |

Конфигурируемые блоки ввода-вывода состоят из входных и выходных буферов с тремя состояниями и выходами с открытым коллектором. Полярность выходного сигнала может быть задана в конфигурации, также в некоторых пределах может быть отрегулирована скорость нарастания и спада сигнала на выходе – так называемые медленные или быстрые выходы. Также обычно в блоки ввода-вывода входят регистры-защелки. Обычно защелки устанавливаются непосредственно возле входных линий; таким образом, задержка распространения сигнала до регистра очень мала, что в итоге уменьшает время реакции всей схемы на изменение входного сигнала. Аналогично, при работе на выход защелки позволяют организовать тактируемый выход сигнала практически сразу на линии вывода.

Предупреждая последствия задержки распространения сигнала, на кристалле ППЛМ создается иерархическая система соединительных линий, в которой длинные линии выступают в качестве сигнальных шин и служат для соединения КЛБ, находящихся физически далеко друг от друга. Короткие линии соединяют КЛБ, расположенные рядом. Коммутационные матрицы, аналогичные матрицам в ПЛИС, соединяют шины и локальные связи требуемым образом. Программируемые ключи внутри кристалла позволяют соединять КЛБ с шинами, объединять шины, соединять шины и локальные связи КЛБ, и осуществлять иные подобные коммутационные операции.

Шины создаются с использованием тристабильных буферных элементов. Тактирующие сигналы распространяются в ППЛМ по специализированным линиям, называемым глобальными тактовыми линиями, которые специально оптимизированы по уровням наводок и шумов и обладают низким импедансом. Они подведены к тактовым буферам и к каждому тактируемому элементу КЛБ.

Технологии реализации ППЛМ

Традиционно ППЛМ разделяют по технологии памяти, применяющейся для хранения логической конфигурации ППЛМ. На сегодня популярны четыре технологии, каждая из которых имеет свои достоинства и недостатки:

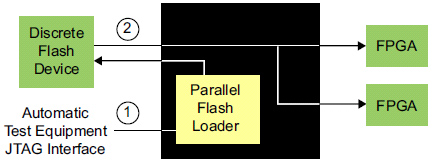

ППЛМ на базе ОЗУ хранят конфигурацию в статической памяти, организованной как массив регистров-защелок. Данный тип ППЛМ требует загрузки конфигурации каждый раз при включении питания и загрузке системы. Существует две базовых модели программирования ППЛМ в данном случае:

ППЛМ с конфигурационной ОЗУ и встроенной памятью не нуждаются в инициации – при включении ПЛЛМ считывает конфигурацию из предварительно запрограммированной встроенной Flash-памяти.

ППЛМ полностью на Flash-памяти также нуждаются только в первоначальной прошивке конфигурации. Дополнительным плюсом данной технологии является меньшее по сравнению с ППЛМ с ОЗУ энергопотребление и более высокая устойчивость к воздействию таких внешних негативных факторов, как радиация.

Современные ППЛМ на базе ОЗУ имеют высокую плотность размещения элементов, однако потребляют значительное количество энергии и нуждаются во внешней энергонезависимой памяти для хранения своей конфигурации. ППЛМ на ОЗУ с встроенной Flash-памятью не нуждаются во внешней памяти. ППЛМ на Flash и однократно программируемые ППЛМ имеют меньшее потребление по сравнению с их аналогами с конфигурационной ОЗУ.

Процессорные ядра

Хотя программируемые устройства были созданы для замены схем на дискретной логике, по мере роста плотности размещения транзисторов на кристалле производители ППЛМ и ПЛИС начали добавлять в кристаллы специализированные узлы в дополнение к КЛБ. В результате получилась так называемая система-на-программируемом-кристалле (System on a Programmable Chip, SoPC), представляющая собой совокупность достаточно сложных устройств (таких как процессорные ядра), интегрированных в единую программируемую систему.

На сегодняшний день практически все ведущие производители ППЛМ и ПЛИС предлагают семейства продуктов с функциональностью микропроцессорных ядер или специализированных IP-ядер. Использование процессорных ядер позволяет разработчикам использовать привычные инструменты, ОС и планировать производительность будущей системы.

Существует два типа ядер – аппаратные (hard) и программные (soft). Программные ядра описываются в виде набора логических функций и обычно представляют собой исходные коды на языке описания аппаратуры (HDL). Аппаратные процессорные ядра называются встроенными, располагаются на одном кристалле с ресурсами программируемой логики и могут использовать эти ресурсы в процессе работы.

Программные ядра имеют два варианта поставки. Первый, и наиболее распространенный – используется одно из ядер, предлагаемых и/или поддерживаемых производителем (разработчик при этом должен самостоятельно добавлять к нему модули ввода-вывода и периферийные устройства). Альтернативный путь – разработчик имеет возможность приобрести исходный HDL-код и уже его интегрировать в разрабатываемую ППЛМ-систему (прим. переводчика – одна из тенденций среди разработчиков ППЛМ-систем – реализация собственных небольших процессорных ядер, например, стековые процессорные ядра, они же форт-ядра, вплоть до многопотоковых ядер).

Для уменьшения времени разработки и облегчения жизни системных программистов производители логики предлагают широкий выбор популярных микропроцессорных ядер. К примеру, Altera предлагает ARM-ядра, Freescale Semiconductor и Intel – реализации программных ядер Nios, NiosII (прим. переводчика – достаточно интересное и расширяемое решение в области софт-ядер представляет ядро MIPSfpga).

Семейство PSoC 5 производства компании Cypress Semiconductor интегрирует конфигурируемую аналоговую и цифровую периферию, память и микроконтроллер. PSoC 5 содержит процессорное ядро ARM Cortex M3 67 МГц, PSoC 4 – ARM Cortex M0, а PSoC 3 – популярное микроконтроллерное ядро 8051 (прим. переводчика – семейство Zynq производства компании Xilinx включает два процессорных ядра ARM Corteх A9).

Преимущества систем-на-программируемом-кристалле

Есть несколько веских причин выбрать для разработок SoPC со встроенным процессорным ядром. Первая – понять скрытые преимущества совместного использования выделенного процессорного ядра и программируемой логики. В том случае, если, к примеру, микроконтроллер не имеет достаточных ресурсов периферийных устройств или линий ввода-вывода, придется компенсировать это добавлением внешней логики или устройств. Даже несмотря на богатый выбор микропроцессорных устройств с их набором разнообразной периферии, они не обладают достаточной гибкостью в случае изменения требований по периферийным интерфейсам или иному функционалу.

Проектирование схемы на новом контроллере или более мощной версии контроллера – достаточно дорогое занятие, требующее дополнительных временных затрат. Конечно, производители контроллеров предлагают в своих решениях достаточно мощные версии с большим набором периферийных устройств, но это имеет оборотную сторону – увеличение стоимости, что может негативно сказаться на стоимости конечного продукта.

SoPC решают данные проблемы. Кристалл может быть запрограммирован или перепрограммирован практически как угодно в процессе разработки системы (при этом топология печатной платы и/или конфигурация внешних устройств могут оставаться неизменными). Это позволяет сократить время выхода продукта на рынок. Некоторые SoPC могут быть полностью или частично перепрограммированы непосредственно в процессе работы конечного устройства.

Риски при разработке сводятся к минимуму благодаря возможностям всестороннего тестирования, обновления и верификации прошивки. Возможен запуск и реконфигурация SoPC непосредственно в составе конечного изделия и в реальных условиях работы для сведения вероятности ошибок разработки к минимуму.

Для SoPC разработка системного программного обеспечения также может быть существенно сокращена. Использование инструментов от производителей ППЛМ позволяет легко обнаруживать ошибки и проверять изделия на совместимость. Если требуемая функциональность или производительность не могут быть достигнуты программно, они реализуются аппаратно на блоках программируемой логики и легко интегрируются с процессорным ядром. Устройства на базе SoPC могут быть модифицированы и проверены на требуемую функциональность с минимальными затратами и практически на любом этапе разработки продукта. В дополнение к практически безграничным возможностям прототипирования, многие SoPC могут быть использованы и для массового производства.

Пример – SoPC в автомобильной электронике

Электронные системы практически любого современного автомобиля имеют поистине неограниченный аппетит в плане потребления ресурсов и количества встроенных микроконтроллеров и процессоров (прим. переводчика – еще в 1990-х на борту среднего автомобиля насчитывалось до двадцати процессоров/ контроллеров, объединенных в сеть). Каждая крупная подсистема автомобиля – управление двигателем, торможением, мультимедийная система – имеет как минимум один микропроцессор в своем составе. Традиционно для каждой из подсистем применялись специализированные микропроцессоры, но количество интеллектуальных подсистем постоянно возрастает, и стратегия разработки специализированного микроконтроллера для каждой из них проблематична. Производителям автомобильной электроники требуются гибкие высокопроизводительные решения, и во многих случаях ППЛМ могут им в этом помочь.

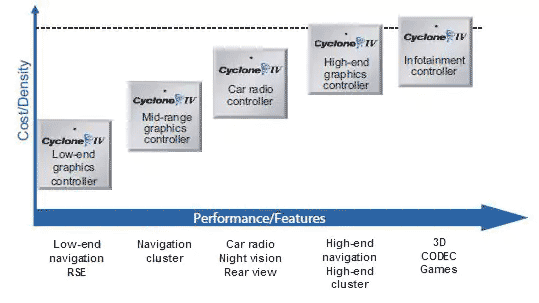

ППЛМ, реализующие графические контроллеры для автомобильных подсистем, уже получили признание, поскольку требования к вычислительной мощности и производительности ввода-вывода постоянно изменяются, а ППЛМ могут быть быстро и без особых затрат переконфигурированы для удовлетворения новых потребностей. Рис. 4 иллюстрирует возможности семейства ППЛМ Altera Cyclone IV в решении задач для различных автомобильных подсистем.

| |

| Рис. 4. | Пример семейства ППЛМ Altera Cyclone IV как эффективного решения для различных задач в области автомобильных графических систем. |

Для каждой задачи программное процессорное ядро NiosII может быть автоматически сгенерировано в соответствии с текущими требованиями разработчика. Необходимые настройки осуществляются через инструментарий SOPC Builder среды QuartusII. Он позволяет настроить и реализовать нужный функционал и сгенерировать необходимую вспомогательную логику.

Nios II является 32-битным RISC-ядром с раздельными шинами адреса и данных. Обе шины имеют свой собственный кэш. Однако окончательное решение остается за разработчиком – шины можно сконфигурировать и на использование общего кэша. В зависимости от требований приложения отдельные узлы процессорного ядра могут отличаться по конечной реализации. К примеру, настраивается использование аппаратных умножителей/ делителей, сдвиговых регистров, вплоть до подмножества поддерживаемых в данной задаче инструкций – все это влияет на производительность процессорного ядра и объем ресурсов ППЛМ, задействованных в его реализации. Аналогично могут настраиваться кэши инструкции и данных – размеры, варианты использования.

Заключение

Чрезвычайно гибкие решения, предлагаемые SoPC, дают разработчикам возможность разработать микроконтроллер, оптимальный для конкретной задачи. Чип может быть запрограммирован и перепрограммирован в процессе разработки по мере необходимости, что позволяет существенно сократить время на прототипирование конечного устройства и, в итоге, ускорить выход продукта на рынок. Испытания устройства могут выполняться практически сразу после завершения процесса разработки или, во многих случаях, параллельно ему. Более того, изменения могут быть внесены непосредственно во время полевых испытаний и даже после установки SoPC в конечный продукт.

Статью подготовил и перевел Калачев Александр, г. Барнаул,

по материалам журнала «Electronics information update».